# 20V, 10A, Synchronous Boost Converter with Load Disconnect Control

## **Description**

The FH43050 is a 20.0V synchronous boost(step-up) converter with the gate driver built-in for load disconnect. The FH43050 integrates two low on resistance power MOSFET: A 7.0mohm switching FET and a 7.0mohm rectifier MOSET.

The FH43050 uses the adaptive constant off time peak current mode control. The FH43050 operates in force continues mode to avoid audible noise under light load.

The FH43050 includes configurable features include programmable cycle-by-cycle current limit and programmable switching frequency functions.

The FH43050 could isolate the output from input side when shutdown. Once the output is shorted, it enters into the hiccup mode to lower the thermal stress and can recover automatically after the short condition releases.

Additionally, the FH43050 also has OVP and thermal protection to avoid the fault operation. The FH43050 is in a 3.0mm\*3.5mm 13-pin VQFN package with enhanced thermal dissipation.

# **Typical Application Schematic**

#### I...... W.14.... D...... 2

Features

- Input Voltage Range: 2.7V to 20.0V

- Output Voltage Range: 4.5V to 20.0V

- Minimal Boost Ratio is down to 1.0

- Efficiency up to 96%:

V<sub>IN</sub> =7.2V, V<sub>BUS</sub> =16.0V, I<sub>OUT</sub> =2.0A

- Two  $7m\Omega$  MOSFETs Integrated

- Adjustable switching frequency up to 2.2MHz

- Programmable Cycle-by-Cycle Current Limit up to 15.0A

- Hiccup Short Protection with Load Disconnect Drive

- FCCM Operation under light load

- Input Under-Voltage Lockout

- Output Over-Voltage Protection at fixed 21.0V

- Over-Temperature Protection

- Package: VQFN13-3.0\*3.5

## **Applications**

- Portable POS terminal

- Bluetooth Speaker

- E-Cigarette

- Thunderbolt Interface

- USB Type-C Power Delivery

Output Current (A)

### MARKING INFORMATION

NOTE: X X X X X = Date Code, Trace Code and Vendor Code. VIN□ CBST XXXXXVendor Code  $\mathbf{C}_{\mathrm{IN}}$ Trace Code Date Code - Year BST SW VOUT P-FET (option) **VBUS**  $V_{OUT} = V_{FB} \times \left(1 + \frac{R_{UP}}{R_{DOWN}}\right)$ CBUS OFF  $\geq \mathbf{R}_{\text{DOW}}$ DISDRY 🗅 FREQ FB ☐ RFREQ Efficiency vs. Output Current ILIMIT COMP **R**ILIMIT ≥ VCC AGND **PGND**  $\mathbf{C}_{\mathrm{C}}$ 70  $\mathbf{R}_{C}$ Figure. 1 Application Schematic 20 0.0001

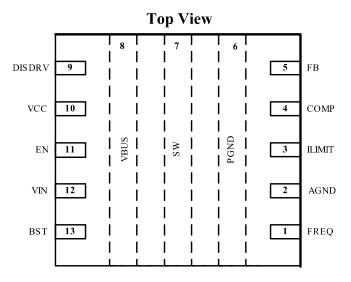

# **Pin Configuration**

Figure 2. Pin Function (VQFN-13L)

## **Pin Functions**

| Pin    |        | D 1.4                                                                                                                                                                                             |  |  |  |

|--------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Number | Name   | Description                                                                                                                                                                                       |  |  |  |

| 1      | FREQ   | The switching frequency is programmed by a resistor between this pin and the AGND. This pin can't be float in application.                                                                        |  |  |  |

| 2      | AGND   | Analog ground.                                                                                                                                                                                    |  |  |  |

| 3      | ILIMIT | A Adjustable LSFET peak current limit. Connect a resistor to AGND.                                                                                                                                |  |  |  |

| 4      | СОМР   | Output of internal error amplifier, loop compensation network connect to COMP and AGND COMP is a sensitive node, keep COMP away from SW and BST pin.                                              |  |  |  |

| 5      | FB     | Feedback Input. FB senses the output voltage, connect FB with a resistor divider connected between the output and ground. FB is a sensitive node, keep FB away from SW and BST pin.               |  |  |  |

| 6      | PGND   | Power ground. The source of LSFET connect to PGND internally.                                                                                                                                     |  |  |  |

| 7      | SW     | Power switching pin of boost converter, common node of LSFET drain and HSFET source.  Connect the coil to this pin and power input.                                                               |  |  |  |

| 8      | VBUS   | Output pin of boost converter, connect to the drain of HSFET internally.                                                                                                                          |  |  |  |

| 9      | DISDRV | A gate drive output for the external disconnect FET. Connect the DISDRV pin to the gate of the external FET. Leave it floating if not using the load disconnect function.                         |  |  |  |

| 10     | VCC    | Output of internal regulator, A ceramic capacitor of more than 4.7uF is required between this pin and ground.                                                                                     |  |  |  |

| 11     | EN     | Enable pin. Pull high to turn on the IC, don't float.                                                                                                                                             |  |  |  |

| 12     | VIN    | Input supply pin. Bypass Vin to GND with a large capacitor and at least another 0.1uF ceramic capacitor to eliminate noise on the input to the IC.  Put the capacitors close to Vin and GND pins. |  |  |  |

| 13     | BST    | Boot strap pin Connect a 0.1uF or greater capacitor between and BST to power the high side gate driver.                                                                                           |  |  |  |

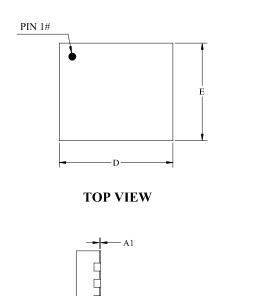

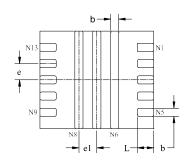

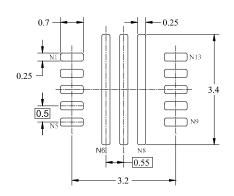

# **Packaging Information**

Type: VQFN3.0\*3.5-13L

**BOTTOM VIEW**

SIDE VIEW

**RECOMMENDED LAND PATTERN** (Unit: mm)

| Symbol | Dimensions In Millimeters |        |        |  |  |

|--------|---------------------------|--------|--------|--|--|

| Symbol | MIN                       | MOD    | MAX    |  |  |

| A      | A 0.700                   |        | 0.800  |  |  |

| A1     | 0.000                     | 0.02 0 | 0.050  |  |  |

| A2     | 0.203 REF                 |        |        |  |  |

| b      | 0.200                     | 0.250  | 0.3 00 |  |  |

| D      | 3.45 0                    | 3.5 00 | 3.550  |  |  |

| E      | 2.95 0                    | 3.000  | 3.050  |  |  |

| L      | 0.45 0                    | 0.500  | 0.550  |  |  |

| e      | 0.5 00 BSC                |        |        |  |  |

| e1     | 0.55 0 BSC                |        |        |  |  |

NOTE: This drawing is subject to change without notice.

## ORDERING INFORMATION

| Part Number | Voltage Range | Features                                                                                                                                                                                            | Operating<br>Temperature | Package Type    | Top Mark            | SPQ          |

|-------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-----------------|---------------------|--------------|

| FH43050N13  | 2.7V ~ 20.0V  | <ul> <li>Synchronous Boost(Step-up)</li> <li>96% Efficiency</li> <li>VFB Voltage: 1.2V</li> <li>Vout: 4.5V~20.0V(ADJ)</li> <li>Switching Frequency: 2.2MHz</li> <li>Current Limit: 15.0A</li> </ul> | -40°C to 85°C            | VQFN3.0*3.5-13L | FH43050<br>YY MM LL | 3000PCS/Reel |

#### Note:

- > FH43050 devices are Pb-free and RoHs compliant.

- > The surface prints of our semiconductor devices are subject to change during the production process and do not involve changes in electrical parameters, and we will not separately state the notice.

- > If you have any other custom purchase needs, please contact our sales department.

- > ForDevices reserves the right to amend and legally interpret the electrical parameters of this chip device.

#### ESD SENSITIVITY CAUTION

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

### Note:

- The information described herein is subject to change without notice.

- > ForDevices Inc. is not responsible for any problems caused by circuits or diagrams described herein whose related industrial properties, patents, or other rights belong to third parties. The application circuit examples explain typical applications of the products, and do not guarantee the success of any specific mass-production design.

- > Use of the information described herein for other purposes and/or reproduction or copying without the express permission of ForDevices Inc. is strictly prohibited.

- > The products described herein cannot be used as part of any device or equipment affecting the human body, such as exercise equipment, medical equipment, security systems, gas equipment, or any apparatus installed in airplanes and other vehicles, without prior written permission of ForDevices Inc.

- Although ForDevices Inc. exerts the greatest possible effort to ensure high quality and reliability, the failure or malfunction of semiconductor products may occur. The user of these products should therefore give thorough consideration to safety design, including redundancy, fire-prevention measures, and malfunction prevention, to prevent any accidents, fires, or community damage that may ensue.

▲ Update by Jul.2020